|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

您所在位置是:

附件材料>设计报告>2.数字滤波器设计 数字示波器设计

摘 要 本系统提出了一种基于现场可编程门阵列(FPGA)和51单片机技术实现液晶数字示波器的技术途径。设计方案中选用ALTERA公司的FLEX10K20逻辑可编程芯片,采用VHDL语言设计实现A/D转换驱动、频率测量与控制、幅度测量与控制、RAM存储、数字滤波,以AT89C51单片机实现了液晶显示和键盘扫描功能,并完成了FPGA与单片机接口电路的程序设计。在编程时采用QUARTUS II仿真综合软件对程序进行了逻辑综合、时序仿真以及优化。设计完成的数字示波器具有波形显示、频率测量、幅度测量、键盘控制垂直灵敏度与扫描速度等功能,并具有体积小、携带方便、以电池供电等特点。

一、总体方案设计 本设计要求完成一个被测周期信号的频率范围为10Hz~10MHz, 实时采样速率≤1MSa/s,等效采样速率≥200MSa/s的数字示波器,对数据采集与处理的实时性及速度要求很高,鉴于此,本设计的数据采集使用AD7821模数转换芯片,数据处理使用FPGA,用VHDL硬件描述语言编程完成。显示使用启东公司的LJD-IV+液晶/键盘显示模块,LJD-IV+液晶/键盘显示模块自带汉字库、接触式按键、各种画点画线画图命令、光标显示、画面移位、睡眠模式等功能,用AT89C51单片机实现液晶显示与键盘控制。 本方案的整体结构如图1所示,输入信号经输入电路变换(放大或衰减)分为两路,一路经触发电路产生触发信号,进一步测量频率并产生控制信号;另一路经取样保持电路,再进行AD转换与数据存储,进一步计算V-pp, 最后将测量结果送入输入与显示控制电路(扫描键盘,驱动液晶)完成显示。以4*4矩阵键盘为输入设备,经51单片机将控制信息送往FPGA进而调节输入电路参数。

SHAPE \* MERGEFORMAT

图1 系统原理框图 二、系统硬件设计与实现 2.1 系统电路图 图2为系统设计顶层结构图,描述了FPGA模块,AT89C51模块,AD7821模块及LJD-IV+液晶/键盘显示模块之间的接口。

2.2极性变换模块 一般所要测量的信号多为双极性,由于本系统中没有-5V的电源,需要在A/D转换前对输入信号进行处理,把双极性信号转换成单极性,处理电路如图3所示。Vi=(Vin+5V)/2,当Vin=-5V时,Vi=0V;当Vin=5V时,Vi=5V。经过这样处理后,输入信号可由双极性波转换成单极性波,输入电压Vin的范围拓宽到-5V~+5V,幅度测量范围也有所拓展,但测量精度有所下降。

2.2增益控制模块

2.3触发电路模块 2.3.1原理分析 将输入信号通过触发模块(含有比较器),一周期的输入信号得到一上升沿触发。 2.3.2原理电路 如图4所示,将输入信号接入比较器LM339的正极,负极接入一可通过滑动变阻器微调的电压,通过与8脚电压比较,得到一个周期与输入信号相同的方波,作为触发信号送给FPGA。该触发模块电路的基本原理如右图所示。

2.4数据处理 2.4.1频率测量 频率测量的基本原理是计算在1S的时钟周期内测频信号的周期数。当系统正常工作时,脉冲发生器提供1 Hz的输入信号,经过测频控制信号发生器进行信号的变换后产生计数信号,被测信号通过触发电路产生同频率的脉冲信号,送入计数模块,计数模块对输入的脉冲信号进行计数,将计数结果送入锁存器中,然后再送入液晶显示。

图5 频率测量原理图

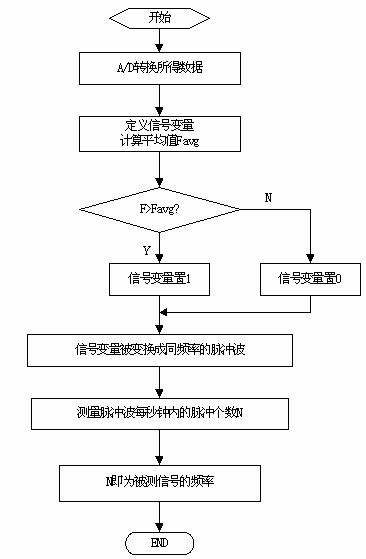

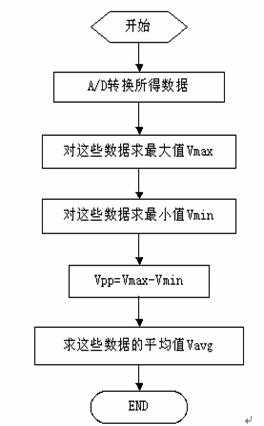

2.4.2 幅度测量 幅度测量的思路是计算A/D转换所得数据的最大值和最小值,计算时把这些数据定义成一个数组,再计算这个数组的最大值和最小值,最大值减去最小值就是波形数据的峰峰值;把这些数组求和后再除以数据总数即为数组的平均值。 2.4.3扫描速度调节 频率调节用来展宽或压缩时间轴,分4个档位。当为3档时,时间轴保持原始长度,设此时所显示的波形为T时间内的波形,波形全部显示在液晶上;当为2档时,使得所显示的波形为T/2时间内的波形全部显示在液晶上,相当于时间轴被拉伸2倍;当为1档时,使得所显示的波形为T/4时间内的波形全部显示在液晶上,相当于时间轴被拉伸4倍;当为0档时,使得所显示的波形为T/8时间内的波形全部显示在液晶上,相当于时间轴被拉伸8倍。 2.4.4垂直灵敏度调节 幅度调节用来调节幅度轴,分7个档位。当为6档时,对A/D转换所得的8位二进制数后补3个0,相当于对这个8位二进制数乘以8,幅度轴被放大了8倍;当为5档时,对8位二进制数后补2个0,相当于对这个8位二进制数乘以4,幅度轴被放大了4倍;当为4档时,对8位二进制数后补1个0,相当于对这个8位二进制数乘以2,幅度轴被放大了2倍;当为3档时,对这个8位二进制数不作处理,幅度轴即为原始幅度;当为2档时,对这个8位二进制数前补1个0,相当于对这个8位二进制数乘以1/2,幅度轴缩小为原来的1/2;当为1档时,对这个8位二进制数前补2个0,相当于对这个8位二进制数乘以1/4,幅度轴缩小为原来的1/4;当为0档时,对这个8位二进制数前补3个0,相当于对这个8位二进制数乘以1/8,幅度轴缩小为原来的1/8。 三、系统软件设计与实现 软件系统的主要任务是通过FPGA读取由外部硬件设备传输来的数据,排除干扰信号、将显示数据送单片机进行显示,并进行波形的存储与分析。 3.1频率测量流程图

图6 频率测量流程图 图7 幅度测量流程图 测量频率就是计算每秒钟内待测信号的脉冲个数,上面的流程图就实现了这一算法,如图5所示。本系统测频的门闸信号是1Hz,所以所测频率的最小单位就是Hz,由于FPGA的速度快,所测低频是十分准确的。 3.2幅度测量流程图 幅度测量就是把AD转换的数据先存在FPGA内部RAM中,然后在从RAM中读数据的时候把最大值和最小值找出来,最大值减去最小值就是波形数据的峰峰值;把这些数组求和后再除于数据总数即为数组的平均值。 3.3 液晶显示流程图

图8 液晶显示流程图 .3.4 等效采样原理 等效时间采样指的是示波器把多次采集(多次触发)采集到的波形拼凑成一个波形,每次采样速度可能很慢,两次采集触发有一定的偏移,最后形成的两个点间的最小采样间隔的倒数称为等效采样速度.其指标可以达到很高,如1ps 四、系统测试及数据分析 4.1 抗干扰处理 在硬件抗干扰处理上采用电源滤波, 在电路设计中做到了布局紧密,避免了交叉布;在软件抗干扰处理上采用软件陷阱技术,当CPU受到干扰后,往往将一些操作数当作指令码来执行,造成程序执行混乱。这时,首先要尽快将程序纳入正轨(执行真正的指令序列)。软件陷阱就是用一条引导指令强行将捕获的程序引向一个指定的地址,在那里有一段专门对程序出错进行处理的程序,以使程序按既定目标执行。 4.2 直流信号测量数据(测幅范围:-5V~+5V) 表1: 直流信号测量数据表

由表1可以看出:正误差出现了9次,负误差出现了10次,两者基本相等,绝对误差平均值为-3mv,基本为0,属于随机误差。绝对误差都在80mv之内,在测量精度40mv的情况下,属于正常范围。相对误差也比较小,除了前两组,基本都在3%之内。前两组相对误差大是因为信号幅度较小,而测量精度差等原因所造成。 4.3交流信号测量数据 4.2.1幅度测量(信号频率为1000Hz,测幅范围:0~10V) 由表2可知交流1000Hz信号输入时,在信号幅度为0V~5V时测量误差比较小,在5V~10V时,测量误差比较大,属于系统误差,还需要做一些矫正处理。以上绝对误差平均值为87mv,相对误差平均值为0.87%。 由表3可知,当幅度一定时,频率的测量比较准确,测量误差比较小。

表2: 幅度测量数据表

表3:频率测量数据表

由以上三组数据可以得出,示波表测量范围为:直流信号-5V~+5V之间;交流信号测量范围为频率1Hz~3000Hz最小最大值介于-5V~+5V之间的信号。 4.2.2频率测量(信号幅度为4V) 附录: 1. AD转换流程图 AD转化采用VHDL的状态机方式在高速时钟的驱动下,AD的速度有多快,系统就可以工作多快,所以最大限度的发挥了AD转换的速度。使用RUN和RUN1可以实现AD速度的控制,用来降低AD速度,采集频率教低的信号波形数据。

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

校址:兰州市安宁东路967号 邮编:730070

Email:yulongbai@gmail.com

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||